# HIGH-SPEED 3.3V IDT70V659/58/57S 128/64/32K x 36 ASYNCHRONOUS DUAL-PORT STATIC RAM

# Features

- True Dual-Port memory cells which allow simultaneous access of the same memory location

- High-speed access

- Commercial: 10/12/15ns (max.)

- Industrial: 12/15ns (max.)

- Dual chip enables allow for depth expansion without external logic

- IDT70V659/58/57 easily expands data bus width to 72 bits or more using the Master/Slave select when cascading more than one device

- M/S = VIH for BUSY output flag on Master,

M/S = VIL for BUSY input on Slave

- Busy and Interrupt Flags

- On-chip port arbitration logic

- Full on-chip hardware support of semaphore signaling between ports

- Fully asynchronous operation from either port

- Separate byte controls for multiplexed bus and bus matching compatibility

- Supports JTAG features compliant to IEEE 1149.1

- LVTTL-compatible, single 3.3V (±150mV) power supply for core

- LVTTL-compatible, selectable 3.3V (±150mV)/2.5V (±100mV) power supply for I/Os and control signals on each port

- Available in a 208-pin Plastic Quad Flatpack, 208-ball fine pitch Ball Grid Array, and 256-ball Ball Grid Array

- Industrial temperature range (-40°C to +85°C) is available for selected speeds

- Green parts available, see ordering information

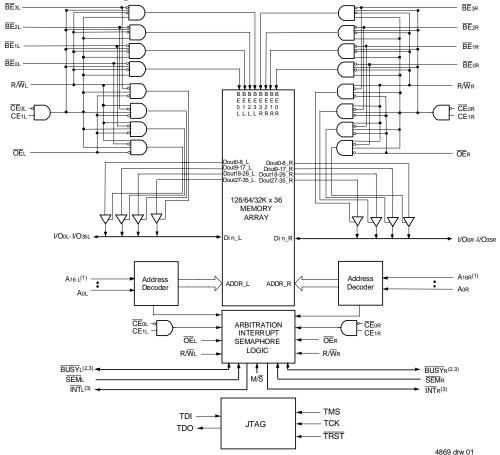

# Functional Block Diagram

### NOTES:

- 1. A16 is a NC for IDT70V658. Also, Addresses A16 and A15 are NC's for IDT70V657.

- 2. BUSY is an input as a Slave (M/S=VIL) and an output when it is a Master (M/S=VIH).

- 3. BUSY and INT are non-tri-state totem-pole outputs (push-pull).

### Description

The IDT70V659/58/57 is a high-speed  $128/64/32K \times 36$  Asynchronous Dual-Port Static RAM. The IDT70V659/58/57 is designed to be used as a stand-alone 4/2/1Mbit Dual-Port RAM or as a combination MASTER/SLAVE Dual-Port RAM for 72-bit-or-more word system. Using the IDT MASTER/SLAVE Dual-Port RAM approach in 72-bit or wider memory system applications results in full-speed, error-free operation without the need for additional discrete logic.

This device provides two independent ports with separate control,

address, and I/O pins that permit independent, asynchronous access for reads or writes to any location in memory. An automatic power down feature controlled by the chip enables (either  $\overline{CE}0$  or CE1) permit the on-chip circuitry of each port to enter a very low standby power mode.

The 70V659/58/57 can support an operating voltage of either 3.3V or 2.5V on one or both ports, controlled by the OPT pins. The power supply for the core of the device (VDD) remains at 3.3V.

# Recommended DC Operating Conditions with Vppo at 2.5V

| Symbol | Parameter                                                       | Min.                | Тур. | Max.                        | Unit |

|--------|-----------------------------------------------------------------|---------------------|------|-----------------------------|------|

| VDD    | Core Supply Voltage                                             | 3.15                | 3.3  | 3.45                        | V    |

| VDDQ   | I/O Supply Voltage <sup>(3)</sup>                               | 2.4                 | 2.5  | 2.6                         | ٧    |

| Vss    | Ground                                                          | 0                   | 0    | 0                           | V    |

| VIH    | Input High Voltage <sup>(3)</sup><br>(Address & Control Inputs) | 1.7                 |      | VDDQ + 100mV <sup>(2)</sup> | V    |

| VIH    | Input High Voltage - I/O(3)                                     | 1.7                 |      | VDDQ + 100mV <sup>(2)</sup> | V    |

| VIL    | Input Low Voltage                                               | -0.5 <sup>(1)</sup> | _    | 0.7                         | ٧    |

#### NOTES:

- 1.  $VIL \ge -1.5V$  for pulse width less than 10 ns.

- 2. VTERM must not exceed VDDQ + 100mV.

- To select operation at 2.5V levels on the I/Os and controls of a given port, the OPT pin for that port must be set to Vss (OV), and VDDQX for that port must be supplied as indicated above.

# Capacitance<sup>(1)</sup>

(TA = +25°C, F = 1.0MHz) PQFP ONLY

| Symbol              | Parameter          | Conditions | Мах. | Unit |

|---------------------|--------------------|------------|------|------|

| Cin                 | Input Capacitance  | VIN = 0V   | 8    | pF   |

| Cout <sup>(2)</sup> | Output Capacitance | Vout = 0V  | 10.5 | pF   |

### NOTES:

- These parameters are determined by device characterization, but are not production tested.

- 2. Cout also references Ci/o.

# Recommended DC Operating Conditions with VDDQ at 3.3V

|   | Symbol | Parameter                                                       | Min.                | Тур. | Мах.                        | Unit |

|---|--------|-----------------------------------------------------------------|---------------------|------|-----------------------------|------|

|   | VDD    | Core Supply Voltage                                             | 3.15                | 3.3  | 3.45                        | ٧    |

|   | VDDQ   | I/O Supply Voltage <sup>(3)</sup>                               | 3.15                | 3.3  | 3.45                        | ٧    |

|   | Vss    | Ground                                                          | 0                   | 0    | 0                           | ٧    |

|   | VIH    | Input High Voltage<br>(Address & Control Inputs) <sup>(3)</sup> | 2.0                 | -    | VDDQ + 150mV <sup>(2)</sup> | V    |

| Ī | VIH    | Input High Voltage - I/O <sup>(3)</sup>                         | 2.0                 | _    | VDDQ + 150mV <sup>(2)</sup> | ٧    |

|   | VIL    | Input Low Voltage                                               | -0.3 <sup>(1)</sup> | _    | 0.8                         | ٧    |

#### NOTES:

- 1.  $V_{IL \ge}$  -1.5V for pulse width less than 10 ns.

- 2. VTERM must not exceed VDDQ + 150mV.

- To select operation at 3.3V levels on the I/Os and controls of a given port, the OPT pin for that port must be set to VDD (3.3V), and VDDDX for that port must be supplied as indicated above.

# Maximum Operating Temperature and Supply Voltage<sup>(1)</sup>

| Grade      | Ambient<br>Temperature | GND | VDD                 |

|------------|------------------------|-----|---------------------|

| Commercial | 0°C to +70°C           | 0V  | 3.3V <u>+</u> 150mV |

| Industrial | -40°C to +85°C         | 0V  | 3.3V <u>+</u> 150mV |

4869 tbl 04

#### NOTE:

1. This is the parameter TA. This is the "instant on" case temperature.

# Absolute Maximum Ratings(1)

| Symbol                        | Rating                                   | Commercial<br>& Industrial | Unit |

|-------------------------------|------------------------------------------|----------------------------|------|

| Vterm <sup>(2)</sup><br>(Vdd) | VDD Terminal Voltage with Respect to GND | -0.5 to + 4.6              | V    |

| TBIAS <sup>(3)</sup>          | Temperature Under Bias                   | -55 to +125                | °C   |

| Tstg                          | Storage Temperature                      | -65 to +150                | °C   |

| Тли                           | Junction Temperature                     | +150                       | °C   |

| IOUT(For VDDQ = 3.3V)         | DC Output Current                        | 50                         | mA   |

| IOUT(For VDDQ = 2.5V)         | DC Output Current                        | 40                         | mA   |

4869 tbl 05

#### NOTES

- Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS

may cause permanent damage to the device. This is a stress rating only

and functional operation of the device at these or any other conditions above

those indicated in the operational sections of this specification is not implied.

Exposure to absolute maximum rating conditions for extended periods may

affect reliability.

- VTERM must not exceed VDD + 150mV for more than 25% of the cycle time or 4ns maximum, and is limited to ≤ 20mA for the period of VTERM ≥ VDD + 150mV

- 3. Ambient Temperature under DC Bias. No AC Conditions. Chip Deselected.

# DC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range (VDD = 3.3V ± 150mV)

|            |                                      |                                           | 70V659 | /58/57S |      |

|------------|--------------------------------------|-------------------------------------------|--------|---------|------|

| Symbol     | Parameter                            | Test Conditions                           | Min.   | Max.    | Unit |

| Iu         | Input Leakage Current <sup>(1)</sup> | VDDQ = Max., VIN = 0V to VDDQ             | _      | 10      | μΑ   |

| ILO        | Output Leakage Current               | CE0 = ViH or CE1 = ViL, Vouτ = 0V to VDDΩ | _      | 10      | μΑ   |

| Vol (3.3V) | Output Low Voltage <sup>(2)</sup>    | IOL = +4mA, VDDQ = Min.                   | _      | 0.4     | V    |

| Vон (3.3V) | Output High Voltage <sup>(2)</sup>   | IOH = -4mA, VDDQ = Min.                   | 2.4    | _       | V    |

| Vol (2.5V) | Output Low Voltage <sup>(2)</sup>    | IOL = +2mA, VDDQ = Min.                   | _      | 0.4     | V    |

| Vон (2.5V) | Output High Voltage <sup>(2)</sup>   | IOH = -2mA, VDDQ = Min.                   | 2.0    | _       | ٧    |

NOTE:

1. At  $VDD \le -2.0V$  input leakages are undefined.

2. VDDQ is selectable (3.3V/2.5V) via OPT pins. Refer to p.6 for details.

4869 tbl 09

DC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range<sup>(3)</sup> (VDD = 3.3V ± 150mV)

| ·                               |                                                           | The state of the s |        |   | 70V659/58/57S10<br>Com'l Only |      |                     |      | 70V659/58/57S15<br>Com'l<br>& Ind |      |      |

|---------------------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---|-------------------------------|------|---------------------|------|-----------------------------------|------|------|

| Symbol                          | Parameter                                                 | Test Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Versio | n | Typ. <sup>(4)</sup>           | Max. | Typ. <sup>(4)</sup> | Max. | Typ. <sup>(4)</sup>               | Max. | Unit |

| <b>I</b> DD                     | Dynamic Operating                                         | CEL and CER= VIL,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | COM'L  | S | 340                           | 500  | 315                 | 465  | 300                               | 440  | mA   |

| Current (Both<br>Ports Active)  | Outputs Disabled $f = fMAX^{(1)}$                         | IND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | S      | _ | _                             | 365  | 515                 | 350  | 490                               |      |      |

| ISB1                            | Standby Current                                           | CEL = CER = VIH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | COM'L  | S | 115                           | 165  | 90                  | 125  | 75                                | 100  | mA   |

| (Both Ports - TTL Level Inputs) | $f = fMAX^{(1)}$                                          | IND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | S      | _ |                               | 115  | 150                 | 100  | 125                               |      |      |

| ISB2                            | Standby Current<br>(One Port - TTL                        | CE"A" = VIL and CE"B" = VIH(5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | COM'L  | S | 225                           | 340  | 200                 | 325  | 175                               | 315  | mA   |

|                                 | Level Inputs)                                             | Active Port Outputs Disabled,<br>f=fMAX <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | IND    | S | _                             | _    | 225                 | 365  | 200                               | 350  |      |

| ISB3                            | Full Standby Current<br>(Both Ports - CMOS                | Both Ports $\overline{CE}L$ and $\overline{CE}R \ge VDDQ - 0.2V$ ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | COM'L  | S | 3                             | 15   | 3                   | 15   | 3                                 | 15   | mA   |

|                                 | Level Inputs)                                             | VIN $\geq$ VDDQ - 0.2V or VIN $\leq$ 0.2V, $f = 0^{(2)}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | IND    | S | —                             | _    | 6                   | 15   | 6                                 | 15   |      |

| ISB4                            | Full Standby Current<br>(One Port - CMOS<br>Level Inputs) | $\overline{CE}^*A^* \le 0.2V$ and $\overline{CE}^*B^* \ge VDDQ - 0.2V^{(5)}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | COM'L  | S | 220                           | 335  | 195                 | 320  | 170                               | 310  | mA   |

|                                 | Lever inpuls)                                             | $VIN \ge VDDQ - 0.2V$ or $VIN \le 0.2V$ ,<br>Active Port, Outputs Disabled,<br>$f = fMAX^{(1)}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IND    | S | _                             |      | 220                 | 360  | 195                               | 345  |      |

### NOTES:

- 1. At f = fmax, address and control lines (except Output Enable) are cycling at the maximum frequency read cycle of 1/trc, using "AC TEST CONDITIONS" at input levels of GND to 3V.

- 2. f = 0 means no address or control lines change. Applies only to input at CMOS level standby.

- 3. Port "A" may be either left or right port. Port "B" is the opposite from port "A".

- 4. VDD = 3.3V,  $TA = 25^{\circ}C$  for Typ, and are not production tested. IDD DC(f=0) = 120mA (Typ).

- 5.  $\overline{CE}x = VIL \text{ means } \overline{CE}ox = VIL \text{ and } CE1x = VIH$

- $\overline{CE}x = VIH \text{ means } \overline{CE}0x = VIH \text{ or } CE1x = VIL$

- $\overline{\text{CE}} x \le 0.2 V \text{ means } \overline{\text{CE}} ox \le 0.2 V \text{ and } \text{CE} 1x \ge V \text{DDQ} 0.2 V$

- $\overline{\text{CE}}\text{x} \geq \text{V}_{\text{DDQ}}$  0.2V means  $\overline{\text{CE}}\text{ox} \geq \text{V}_{\text{DDQ}}$  0.2V or CE1x 0.2V

- "X" represents "L" for left port or "R" for right port.

### AC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range<sup>(5)</sup>

|            |                                                | 70V659/58/57S10<br>Com'l Only Com'l<br>& Ind |      | m'l  | 70V659/<br>Co<br>& |      |      |      |

|------------|------------------------------------------------|----------------------------------------------|------|------|--------------------|------|------|------|

| Symbol     | Parameter                                      | Min.                                         | Max. | Min. | Max.               | Min. | Max. | Unit |

| READ CYCLE |                                                |                                              |      |      |                    |      |      |      |

| trc        | Read Cycle Time                                | 10                                           | _    | 12   |                    | 15   | _    | ns   |

| taa        | Address Access Time                            |                                              | 10   | _    | 12                 | _    | 15   | ns   |

| tace       | Chip Enable Access Time <sup>(3)</sup>         | _                                            | 10   |      | 12                 | _    | 15   | ns   |

| tabe       | Byte Enable Access Time <sup>(3)</sup>         |                                              | 5    |      | 6                  | _    | 7    | ns   |

| taoe       | Output Enable Access Time                      | _                                            | 5    |      | 6                  | _    | 7    | ns   |

| tон        | Output Hold from Address Change                | 3                                            |      | 3    |                    | 3    | _    | ns   |

| tLZ        | Output Low-Z Time <sup>(1,2)</sup>             | 0                                            | _    | 0    | -                  | 0    | _    | ns   |

| tHZ        | Output High-Z Time <sup>(1,2)</sup>            | 0                                            | 4    | 0    | 6                  | 0    | 8    | ns   |

| tpu        | Chip Enable to Power Up Time <sup>(2)</sup>    | 0                                            | _    | 0    |                    | 0    | _    | ns   |

| tpD        | Chip Disable to Power Down Time <sup>(2)</sup> | _                                            | 10   |      | 10                 | _    | 15   | ns   |

| tsop       | Semaphore Flag Update Pulse (OE or SEM)        |                                              | 4    |      | 6                  |      | 8    | ns   |

| tsaa       | Semaphore Address Access Time                  | 3                                            | 10   | 3    | 12                 | 3    | 20   | ns   |

4869 tbl 12

# AC Electrical Characteristics Over the Operating Temperature and Supply Voltage<sup>(5)</sup>

|             |                                                    | 70V659/58/57S10<br>Com'l Only |      | 70V659/58/57S12<br>Com'l<br>& Ind |      | 70V659/58/57S15<br>Com'l<br>& Ind |      |      |

|-------------|----------------------------------------------------|-------------------------------|------|-----------------------------------|------|-----------------------------------|------|------|

| Symbol      | Parameter                                          | Min.                          | Max. | Min.                              | Max. | Min.                              | Max. | Unit |

| WRITE CYCLE |                                                    |                               |      |                                   |      |                                   |      |      |

| twc         | Write Cycle Time                                   | 10                            | _    | 12                                | -    | 15                                | _    | ns   |

| tew         | Chip Enable to End-of-Write <sup>(3)</sup>         | 8                             | _    | 10                                | _    | 12                                | _    | ns   |

| taw         | Address Valid to End-of-Write                      | 8                             | _    | 10                                | _    | 12                                | _    | ns   |

| tas         | Address Set-up Time <sup>(3)</sup>                 | 0                             | _    | 0                                 | _    | 0                                 | _    | ns   |

| twp         | Write Pulse Width                                  | 8                             | _    | 10                                |      | 12                                | _    | ns   |

| twr         | Write Recovery Time                                | 0                             | _    | 0                                 |      | 0                                 | _    | ns   |

| tow         | Data Valid to End-of-Write                         | 6                             | _    | 8                                 |      | 10                                | _    | ns   |

| tDH         | Data Hold Time <sup>(4)</sup>                      | 0                             | _    | 0                                 |      | 0                                 | _    | ns   |

| twz         | Write Enable to Output in High-Z <sup>(1,2)</sup>  | _                             | 4    |                                   | 4    | _                                 | 4    | ns   |

| tow         | Output Active from End-of-Write <sup>(1,2,4)</sup> | 0                             | _    | 0                                 |      | 0                                 | _    | ns   |

| tswrd       | SEM Flag Write to Read Time                        | 5                             | _    | 5                                 |      | 5                                 | _    | ns   |

| tsps        | SEM Flag Contention Window                         | 5                             |      | 5                                 |      | 5                                 | _    | ns   |

NOTES:

4869 tbl 13

- 1. Transition is measured 0mV from Low or High-impedance voltage with Output Test Load (Figure 2).

- This parameter is guaranted by device characterization, but is not production tested.

To access RAM, CE= VIL and SEM = VIH. To access semaphore, CE = VIH and SEM = VIL. Either condition must be valid for the entire tew time.

- 4. The specification for ton must be met by the device supplying write data to the RAM under all operating conditions. Although ton and tow values will vary over voltage and temperature, the actual toH will always be smaller than the actual tow.

- 5. These values are valid regardless of the power supply level selected for I/O and control signals (3.3V/2.5V). See page 6 for details.

# AC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range

|             |                                                    | 70V659/58/57S10<br>Com'l Only |      | 70V659/58/57S12<br>Com'l<br>& Ind |      | 70V659/58/57S15<br>Com'l<br>& Ind |      | 11.2 |

|-------------|----------------------------------------------------|-------------------------------|------|-----------------------------------|------|-----------------------------------|------|------|

| Symbol      | Parameter                                          | Min.                          | Max. | Min.                              | Max. | Min.                              | Мах. | Unit |

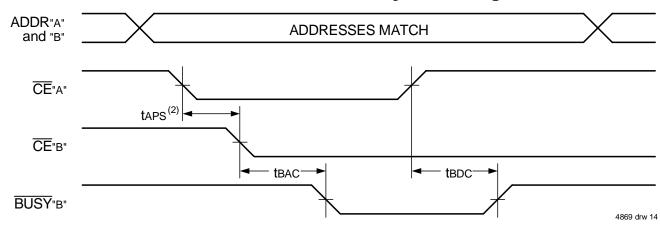

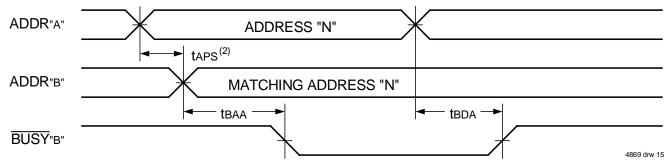

| BUSY TIMING | (M/S=VIH)                                          | •                             |      |                                   |      |                                   |      |      |

| tbaa        | BUSY Access Time from Address Match                |                               | 10   | _                                 | 12   | _                                 | 15   | ns   |

| tBDA        | BUSY Disable Time from Address Not Matched         | _                             | 10   |                                   | 12   |                                   | 15   | ns   |

| tBAC        | BUSY Access Time from Chip Enable Low              |                               | 10   | _                                 | 12   | _                                 | 15   | ns   |

| tBDC        | BUSY Disable Time from Chip Enable High            |                               | 10   | _                                 | 12   | _                                 | 15   | ns   |

| taps        | Arbitration Priority Set-up Time (2)               | 5                             | _    | 5                                 | _    | 5                                 | _    | ns   |

| tBDD        | BUSY Disable to Valid Data <sup>(3)</sup>          | _                             | 10   | _                                 | 12   | _                                 | 15   | ns   |

| twn         | Write Hold After BUSY <sup>(5)</sup>               | 8                             |      | 10                                |      | 12                                | _    | ns   |

| BUSY TIMING | (M/S=VIL)                                          |                               |      |                                   |      |                                   |      |      |

| twB         | BUSY Input to Write <sup>(4)</sup>                 | 0                             |      | 0                                 |      | 0                                 |      | ns   |

| twн         | Write Hold After BUSY <sup>(5)</sup>               | 8                             | _    | 10                                |      | 12                                |      | ns   |

| PORT-TO-POR | T DELAY TIMING                                     |                               |      |                                   |      |                                   |      |      |

| twdd        | Write Pulse to Data Delay <sup>(1)</sup>           |                               | 22   |                                   | 25   | _                                 | 30   | ns   |

| todo        | Write Data Valid to Read Data Delay <sup>(1)</sup> |                               | 20   |                                   | 22   | _                                 | 25   | ns   |

4869 tbl 14

### NOTES:

- 1. Port-to-port delay through RAM cells from writing port to reading port, refer to "Timing Waveform of Write with Port-to-Port Read and BUSY (M/S = Vii)".

- 2. To ensure that the earlier of the two ports wins.

- 3. tbdd is a calculated parameter and is the greater of the Max. spec, twdd twp (actual), or tddd tdw (actual).

- 4. To ensure that the write cycle is inhibited on port "B" during contention on port "A".

- 5. To ensure that a write cycle is completed on port "B" after contention on port "A".

Waveform of **BUSY** Arbitration Controlled by **CE** Timing (M/**S** = VIH)(1)

Waveform of **BUSY** Arbitration Cycle Controlled by Address Match Timing  $(M/\overline{S} = VIH)^{(1)}$

### NOTES:

- 1. All timing is the same for left and right ports. Port "A" may be either the left or right port. Port "B" is the port opposite from port "A".

- 2. If taps is not satisfied, the BUSY signal will be asserted on one side or another but there is no guarantee on which side BUSY will be asserted.

### AC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range

|                  |                      |      | 58/57S10<br>'I Only | 70V659/58/57S12<br>Com'l<br>& Ind |      | 70V659/58/57S15<br>Com'l<br>& Ind |      |      |  |  |

|------------------|----------------------|------|---------------------|-----------------------------------|------|-----------------------------------|------|------|--|--|

| Symbol           | Parameter            | Min. | Max.                | Min.                              | Max. | Min.                              | Max. | Unit |  |  |

| INTERRUPT TIMING |                      |      |                     |                                   |      |                                   |      |      |  |  |

| tas              | Address Set-up Time  | 0    |                     | 0                                 |      | 0                                 | -    | ns   |  |  |

| twr              | Write Recovery Time  | 0    |                     | 0                                 |      | 0                                 |      | ns   |  |  |

| tins             | Interrupt Set Time   | _    | 10                  | _                                 | 12   |                                   | 15   | ns   |  |  |

| tinr             | Interrupt Reset Time | _    | 10                  |                                   | 12   |                                   | 15   | ns   |  |  |

4869 tbl 15

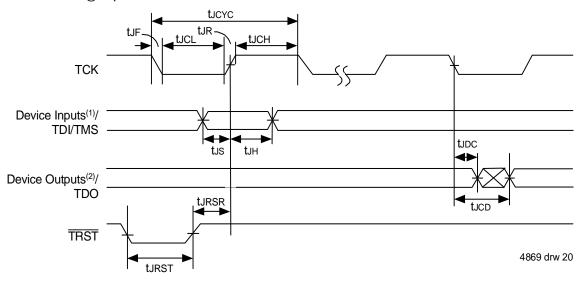

# JTAG Timing Specifications

### NOTES:

- 1. Device inputs = All device inputs except TDI, TMS, and TRST.

- 2. Device outputs = All device outputs except TDO.

### JTAG AC Electrical Characteristics (1,2,3,4)

| Symbol | Parameter               | Min. | Max.             | Units |

|--------|-------------------------|------|------------------|-------|

| tucyc  | JTAG Clock Input Period | 100  | _                | ns    |

| tлсн   | JTAG Clock HIGH         | 40   | _                | ns    |

| tıcı   | JTAG Clock Low          | 40   | _                | ns    |

| tır    | JTAG Clock Rise Time    | _    | 3 <sup>(1)</sup> | ns    |

| ₩      | JTAG Clock Fall Time    | _    | 3 <sup>(1)</sup> | ns    |

| turst  | JTAG Reset              | 50   | _                | ns    |

| tursr  | JTAG Reset Recovery     | 50   | -                | ns    |

| tuco   | JTAG Data Output        | _    | 25               | ns    |

| tudo   | JTAG Data Output Hold   | 0    |                  | ns    |

| tıs    | JTAG Setup              | 15   | _                | ns    |

| tн     | JTAG Hold               | 15   | _                | ns    |

### NOTES:

4869 tbl 19

- 1. Guaranteed by design.

- 2. 30pF loading on external output signals.

- 3. Refer to AC Electrical Test Conditions stated earlier in this document.

- 4. JTAG operations occur at one speed (10MHz). The base device may run at any speed specified in this datasheet.

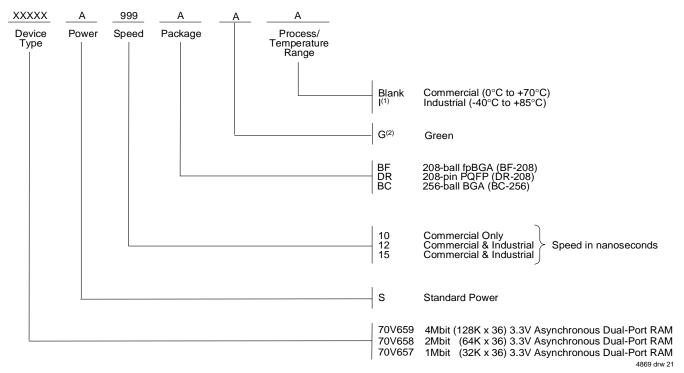

### Ordering Information

### Notes:

- 1. Contact your local sales office for Industrial temp range in other speeds, packages and powers.

- 2. Green parts available. For specific speeds, packages and powers contact your local sales office.